Summary

The overall goal of the project is to develop practical methods to be able to reliably run useful applications on near-term quantum computers. This requires identifying and overcoming the ubiquitous errors that currently limit quantum computing capabilities. Traditional methods of quantifying errors in quantum computers fail to predict how errors affect the output of a quantum computation because the exact impact depends upon the exact form of the noise, additional errors arising from interactions between control mechanisms (e.g., crosstalk) and idle qubits, and how the gates are translated and scheduled into temporal pulses. One promising way to account for global errors is to define a parallel quantum instruction (PQI) to be a set of quantum operations executed in a fixed temporal order, including all idle gates for qubits that are not explicitly targeted by any quantum operation. In this project we develop a general method for reconstructing global noise during a cycle of parallel quantum gates and a framework for mitigating and/or extrapolating errors, leading to an experimental demonstration of their effectiveness. This will enable near-term quantum computers to be used to accurately simulate quantum systems and to determine the accuracy of the simulations.

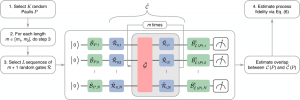

Figure 1. Schematic circuit implementation of the experimental cycle benchmarking protocol for characterizing a noisy parallel quantum instruction G (red). The green gates are used to probe how closely G maps different input states to the desired output state. Random gates (blue) are used to engineer a simple noise model to make the characterization protocol accurate and efficient.

Related Content

Combined momentum- and real-space photoelectric probes of dimensionality-tuned Weyl semimetals

Summary The library of two-dimensional (2D) materials has recently grown to include topological insulators and semimetals. Their incorporation in special device geometries may lead to novel quantum electronics with enhanced functionalities. Weyl semimetals, in particular, offer the most robust form of topological protection. Recent results from our group indicate that Weyl nodes should be […]

March 12, 2019

Entangled States of Beams and their Applications

Summary With David Cory and collaborators at the National Institute of Standards and Technology (NIST) we explore how to engineer beams of neutron or photons that carry entanglement. The degrees of freedom that can be entangled include spin (polarization), momentum, displacement, and angular momentum. These have potential applications ranging from studies of helical internal magnetic fields […]

September 7, 2016

Hybrid Quantum Materials towards Topological Quantum Computing

Summary Proximity engineered hybrid materials have shown promise for topological quantum information processing. This form of quantum computing provides a stable, error-tolerant approach for building scalable quantum information processors. Topological quantum computing relies on braiding non-Abelian particles, such as Majorana fermions, which do not exist in nature. One can however use materials engineering to […]

December 8, 2018

Portable Quantum Dot Measurement System

Summary Detecting heavy metals in water is essential to ensure clean drinking water and appropriate regulatory decisions following an accident (e.g., a spill) or an emergency. Traditionally, high-sensitivity detection of heavy metals requires bulky and costly (to purchase and operate) lab-based instruments. We propose developing a palm-sized, element-specific, highly-sensitive, battery-operated, smartphone-controlled system for on-site measurement […]

July 21, 2022